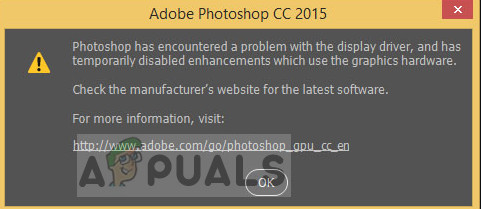

RAMは、実際にはコンピューターで最も重要なコンポーネントの1つですが、購入の決定に関して、他のコンポーネントと同じくらいの考えと労力がRAMに投入されることはめったにありません。通常、一般消費者が気にかけているのは容量だけです。これは正当なアプローチですが、RAMには、保持するメモリのサイズだけではありません。いくつかの重要な要素がRAMのパフォーマンスと効率を決定する可能性があり、おそらくそれらの中で最も重要な要素の2つは周波数とタイミングです。

GSkill TridentZ RGBは、Ryzenシステム用の素晴らしいRAMキットです–画像:GSkill

RAMの周波数は、RAMが実行されると評価されているクロック速度を表すかなり単純な数値です。それは製品ページに明確に記載されており、「高いほど良い」という単純なルールに従います。最近では、3200 Mhz、3600 Mhz、4000 Mhz、またはそれ以上の定格のRAMキットがよく見られます。ストーリーの他のより複雑な部分は、RAMのレイテンシーまたは「タイミング」です。これらは理解するのがはるかに複雑で、一見しただけでは理解しにくいかもしれません。 RAMのタイミングが実際に何であるかを詳しく見ていきましょう。

RAMタイミングとは何ですか?

周波数は最も宣伝されている数値の1つですが、RAMのタイミングは、RAMの全体的なパフォーマンスと安定性にも大きな役割を果たします。タイミングは、RAMチップ上のさまざまな一般的な操作間の遅延を測定します。レイテンシーは操作間で発生する遅延であるため、特定の制限を超えて増加すると、RAMのパフォーマンスに深刻な影響を与える可能性があります。 RAMのタイミングは、RAMがさまざまな操作を実行しているときに発生する可能性のある固有の遅延を表しています。

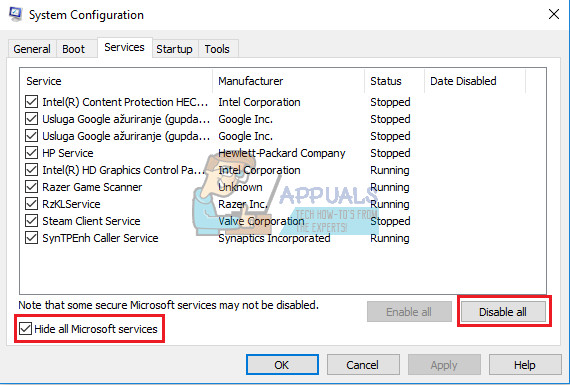

RAMのタイミングはクロックサイクルで測定されます。 16-18-18-38のようなRAMキットの製品ページで、ダッシュで区切られた一連の数字を見たことがあるかもしれません。これらの数値は、RAMキットのタイミングとして知られています。本質的に、それらはレイテンシーを表すので、タイミングに関しては低い方が良いです。これらの4つの数値は、「プライマリタイミング」と呼ばれるものを表しており、レイテンシに最も大きな影響を与えます。他のサブタイミングもありますが、ここでは、プライマリタイミングについてのみ説明します。

4つのプライマリRAMのタイミングは次のように表されます–画像:Tipsmake

一次タイミング

製品リストまたは実際のパッケージには、タイミングは4つの主要なタイミングに対応するtCL-tRCD-tRP-tRASの形式でリストされています。このセットは、RAMキットの実際のレイテンシーに最大の影響を与え、オーバークロック中の焦点でもあります。したがって、文字列16-18-18-38の番号の順序から、どのプライマリタイミングがどの値を持っているかが一目でわかります。

CASレイテンシー(tCL / CL / tCAS)

CASレイテンシー–画像:MakeTechEasier

CASレイテンシは、最も顕著なプライマリタイミングであり、列アドレスをメモリに送信してから応答するデータの開始までのサイクル数として定義されます。これは、最も広く比較され、宣伝されているタイミングです。これは、正しい行がすでに開いている状態で、DRAMからメモリの最初のビットを読み取るのにかかるサイクル数です。 CASレイテンシは、最小値を表す他の数値とは異なり、正確な数値です。この番号は、メモリとメモリコントローラの間で合意する必要があります。

基本的に、CASレイテンシは、メモリがCPUに応答するのにかかる時間です。 CLだけでは考慮できないため、CASについて説明する際に考慮する必要のあるもう1つの要素があります。 CL定格をナノ秒で表される実際の時間に変換する式を使用する必要があります。これはRAMの転送速度に基づいています。式は(CL /転送速度)x 2000です。この式を使用することにより、CL16を使用して3200Mhzで実行されているRAMキットの実際の遅延は10nsであると判断できます。これは、異なる周波数とタイミングのキット間で比較できるようになりました。

RASからCASへの遅延(tRCD)

RASからCASへの遅延–画像:MakeTechEasier

RAS to CASは、読み取り/書き込み操作の潜在的な遅延です。 RAMモジュールはアドレス指定にグリッドベースの設計を使用するため、行番号と列番号の共通部分は特定のメモリアドレスを示します。 tRCDは、行を開いて列にアクセスするために必要な最小クロックサイクル数です。アクティブな行がない状態でDRAMからメモリの最初のビットを読み取る時間は、tRCD + CLの形式で追加の遅延をもたらします。

tRCDは、RAMが新しいアドレスに到達するのにかかる最小時間と見なすことができます。

行のプリチャージ時間(tRP)

行の事前充電時間–画像:MakeTechEasier

間違った行を開く場合(ページミスと呼ばれる)、行を閉じて(プリチャージと呼ばれます)、次の行を開く必要があります。次の行内の列にアクセスできるのは、このプリチャージの後でのみです。したがって、全体の時間はtRP + tRCD + CLに増加します。

技術的には、プリチャージコマンドを発行して1つの行をアイドル状態またはクローズしてから、コマンドをアクティブにして別の行を開くまでの待ち時間を測定します。同じ要因が両方の操作の遅延に影響するため、tRPは2番目の数値tRCDと同じです。

行アクティブ時間(tRAS)

行のアクティブ時間–画像:MakeTechEasier

「ActivatetoPrechargeDelay」または「MinimumRASActive Time」とも呼ばれるtRASは、行アクティブコマンドとプリチャージコマンドの発行の間に必要な最小クロックサイクル数です。これはtRCDと重複しており、SDRAMモジュールの単純なtRCD + CLです。それ以外の場合は、約tRCD + 2xCLです。

tRASは、データを適切に書き込むために行を開いたままにしておく必要がある最小サイクル数を測定します。

コマンドレート(CR / CMD / CPC / tCPD)

オーバークロック中によく見られる、コマンドレートを示す特定の–Tサフィックスもあります。 AMDは、コマンドレートを、DRAMチップが選択されてからコマンドが実行されるまでのサイクル単位の時間として定義しています。これは1Tまたは2Tのいずれかであり、2T CRは、より高いメモリクロックでの安定性または4-DIMM構成に非常に役立ちます。

CRはコマンド期間とも呼ばれます。 1Tの方が高速ですが、特定のシナリオでは2Tの方が安定している可能性があります。また、独自の–T表記にもかかわらず、他のメモリタイミングと同様にクロックサイクルで測定されます。 2つの間のパフォーマンスの違いはごくわずかです。

メモリタイミングの低下の影響

タイミングは一般にRAMキットのレイテンシーに対応するため、RAMのさまざまな操作間の遅延が少ないことを意味するため、タイミングが短いほど優れています。周波数と同様に、応答時間の改善がCPUやメモリ自体の一般的なクロック速度などの他のコンポーネントの速度によって大幅に抑制される収穫逓減のポイントが存在します。言うまでもなく、RAMの特定のモデルのタイミングを下げるには、メーカーによる追加のビニングが必要になる場合があります。そのため、歩留まりが低下し、コストも高くなります。

当然のことながら、RAMのタイミングを短くすると、一般にRAMのパフォーマンスが向上します。次のベンチマークでわかるように、全体的なタイミング(特にCASレイテンシー)が低いほど、少なくともチャート上の数値の点で改善につながります。ゲームをプレイしている間、またはBlenderでシーンをレンダリングしているときに、平均的なユーザーが改善を認識できるかどうかは、まったく別の話です。

コロナベンチマークのレンダリング時間に対するさまざまなRAMのタイミングと周波数の影響–画像:TechSpot

特にCL15を下回った場合、収穫逓減のポイントはすぐに確立されます。この時点で、一般的に、タイミングと遅延はRAMのパフォーマンスを妨げる要因ではありません。レイテンシが収穫逓減のこのポイントに達した場合、周波数、RAMの構成、マザーボードのRAM機能、さらにはRAMの電圧などの他の要因が、RAMのパフォーマンスの決定に関与する可能性があります。

タイミングと頻度

RAMの周波数とタイミングは相互に関連しています。大量生産されているコンシューマーRAMキットで両方の長所を最大限に活用することは不可能です。一般に、RAMキットの定格周波数が高くなると、タイミングが緩くなり(タイミングが長くなり)、それをある程度補います。周波数は一般的にタイミングの影響を少し上回りますが、タイミングが緩くなり全体的なパフォーマンスが低下するため、高周波RAMキットに追加料金を支払っても意味がない場合があります。

この良い例は、DDR4 3200Mhz CL16RAMとDDR43600Mhz CL18RAMの間の議論です。一見すると、3600Mhzキットの方が高速で、タイミングもそれほど悪くないように見えるかもしれません。ただし、CASレイテンシーを説明するときに説明したのと同じ式を適用すると、話は別の方向に進みます。値を式に入れる:(CL /転送速度)x 2000、両方のRAMキットについて、両方のRAMキットの実際の遅延が10nsであるという結果が得られます。はい、他の違いもサブタイミングとRAMの構成方法に存在しますが、同様の全体的な速度により、3600Mhzキットは価格が高いため、より悪い値になります。

さまざまな頻度と待ち時間のベンチマーク結果–画像:GamersNexus

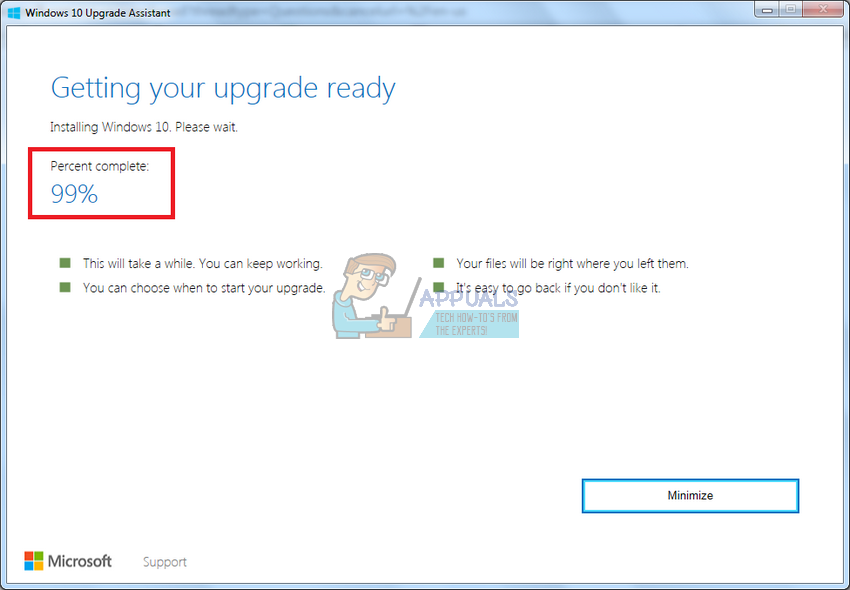

タイミングと同様に、頻度もすぐに収穫逓減のポイントに達します。一般に、AMD Ryzenプラットフォームの場合、DDR4 3600MhzCL16はタイミングと周波数の両方の点でスイートスポットと見なされます。 4000Mhzのようなより高い周波数を使用すると、タイミングが悪化するだけでなく、B450のようなミッドレンジチップセットではマザーボードのサポートでさえ問題になる可能性があります。それだけでなく、Ryzenでは、最良の結果を得るには、Infinityファブリッククロックとメモリコントローラークロックを1:1:1の比率でDRAM周波数と同期させる必要があり、3600Mhzを超えるとその同期が中断されます。これは、待ち時間の増加、一般的な不安定性、および非効率的な周波数につながり、これらのRAMキットを全体的にコストパフォーマンスの悪いものにします。タイミングと同様に、スイートスポットを確立する必要があり、CL16やCL15などのより厳しいタイミングでは、3200Mhzや3600Mhzなどの妥当な周波数を維持するのが最善です。

オーバークロック

RAMのオーバークロックは、PCをいじくり回す場合、最も苛立たしくて気まぐれなプロセスの1つです。熱狂的なファンは、システムからパフォーマンスの最後のビットをすべて絞り出すだけでなく、プロセスがもたらす課題についても、このプロセスを掘り下げてきました。 RAMオーバークロックの基本的なルールは単純です。両方の世界を最大限に活用するには、タイミングを同じに保ちながら、またはタイミングを厳しくしながら、可能な限り高い周波数を達成する必要があります。

RAMはシステムの最も機密性の高いコンポーネントの1つであり、通常、手動で調整する必要はありません。したがって、RAMメーカーには、プラットフォームに応じて「XMP」または「DOCP」と呼ばれるプリロードされたオーバークロックが含まれています。これは、ユーザーがBIOSを介して有効にできる、事前にテストおよび検証されたオーバークロックであると想定されており、多くの場合、これはユーザーが必要とする最適なレベルのパフォーマンスです。

「1usmus」によって作成されたRyzen用のDRAM計算機は、AMDプラットフォームでの手動オーバークロックのための素晴らしいツールです。

手動RAMオーバークロックに挑戦したい場合は、 包括的なRAMオーバークロックガイド 大きな助けになることができます。オーバークロックの安定性テストは、RAMオーバークロックの最も難しい部分です。これは、正しく実行するのに多くの時間と多くのクラッシュが発生する可能性があるためです。それでも、全体の課題は愛好家にとって良い経験になる可能性があり、いくつかのきちんとしたパフォーマンスの向上にもつながる可能性があります。

最後の言葉

RAMは確かに、システムの過小評価されているコンポーネントの1つであり、システムのパフォーマンスと全体的な応答性に大きな影響を与える可能性があります。 RAMのタイミングは、異なるRAM操作間に存在するレイテンシを決定することによって大きな役割を果たします。タイミングを厳しくするとパフォーマンスが向上しますが、収穫逓減のポイントがあり、パフォーマンスの向上を最小限に抑えるために手動でオーバークロックしてタイミングを厳しくするのは少し面倒です。

RAMの値をチェックしながら、RAMの周波数とタイミングの完璧なバランスをとることは、購入を決定する際の最良の方法です。 最高のDDR4RAMキットのおすすめ 2020年には、RAMの選択に関して十分な情報に基づいた決定を下すのに役立つ可能性があります。